# Lecture Notes in Computer Science

5154

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

### **Editorial Board**

**David Hutchison**

Lancaster University, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Alfred Kobsa

University of California, Irvine, CA, USA

Friedemann Mattern

ETH Zurich, Switzerland

John C. Mitchell

Stanford University, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

Oscar Nierstrasz

University of Bern, Switzerland

C. Pandu Rangan

Indian Institute of Technology, Madras, India

Bernhard Steffen

University of Dortmund, Germany

Madhu Sudan

Massachusetts Institute of Technology, MA, USA

Demetri Terzopoulos

University of California, Los Angeles, CA, USA

Doug Tygar

University of California, Berkeley, CA, USA

Gerhard Weikum

Max-Planck Institute of Computer Science, Saarbruecken, Germany

Elisabeth Oswald Pankaj Rohatgi (Eds.)

# Cryptographic Hardware and Embedded Systems – CHES 2008

10th International Workshop Washington, D.C., USA, August 10-13, 2008 Proceedings

### Volume Editors

Elisabeth Oswald University of Bristol Department of Computer Science Merchant Venturers Building, Woodland Road, BS8 1UB, Bristol, UK E-mail: elisabeth.oswald@bristol.ac.uk

Pankaj Rohatgi IBM T.J. Watson Research Center 19 Skyline Drive, Hawthorne, NY 10532, USA E-mail: rohatgi@us.ibm.com

Library of Congress Control Number: 2008931306

CR Subject Classification (1998): E.3, E.4, D.4.6, C.2.0, I.3.1

LNCS Sublibrary: SL 4 – Security and Cryptology

ISSN 0302-9743

ISBN-10 3-540-85052-X Springer Berlin Heidelberg New York ISBN-13 978-3-540-85052-6 Springer Berlin Heidelberg New York

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, re-use of illustrations, recitation, broadcasting, reproduction on microfilms or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media

springer.com

© International Association for Cryptologic Research 2008 Printed in Germany

Typesetting: Camera-ready by author, data conversion by Scientific Publishing Services, Chennai, India Printed on acid-free paper SPIN: 12441693 06/3180 5 4 3 2 1 0

# **Preface**

These are the proceedings of the 10th Workshop on Cryptographic Hardware and Embedded Systems (CHES), held in Washington D.C., USA, August 10–13, 2008. This workshop was sponsored by the International Association for Cryptologic Research (IACR).

The CHES 2008 workshop attracted 107 submissions from 23 countries, of which the program committee selected 27 papers for publication. The review process followed strict standards: each paper received at least four reviews; members of the program committee were restricted to submitting at most two papers. The 42 Program Committee members from 13 countries were selected carefully to ensure that different fields, such as hardware and software implementations, active and passive implementation attacks, cryptanalysis and cryptography including random number generation, embedded systems, and trusted computing, were well represented and a balance between academia and industry was achieved. Counting all Program Committee members, external reviewers, and the Program Co-chairs, we had 158 people contributing to the review process. We would like to thank all Program Committee members and external reviewers for their contribution to the review process.

In just 10 years, the CHES workshop has grown to become the flagship event in its area, attracting high-profile papers and attendees from academia and industry. This excellence is reflected in the quality of the contributed papers and invited talks. In cooperation with the CHES Steering Committee, the Program Committee awarded the CHES 2008 Best Paper Award to two contributions: "Attack and Improvement of a Secure S-box Calculation Based on the Fourier Transform" by Jean-Sébastien Coron, Christophe Giraud, Emmanuel Prouff and Matthieu Rivain, and "Time-Area Optimized Public-Key Engines: MQ-Cryptosystems as Replacement for Elliptic Curves?" by Andrey Bogdanov, Thomas Eisenbarth, Andy Rupp and Christopher Wolf. The purpose of the award is to formally acknowledge excellence in research. We would like to congratulate the authors of these two papers. In addition to presentations of peerreviewed papers there were excellent invited presentations. At the time of compiling the proceedings, an invited talk by Adi Shamir on "RSA: Past, Present and Future", and an invited talk by Ernie Brickell from Intel on "A Vision for Platform Security" had been confirmed.

In order to celebrate the 10th anniversary of CHES, the workshop program included a tour of the National Cryptologic Museum in Fort Mead and a talk by Christof Paar and Çetin Kaya Koç on the history of CHES. In addition there was a rump session and a panel discussion. Special thanks for making these possible and taking care of the local organization go to the General Cochairs Kris Gaj and Jens-Peter Kaps (both from George Mason University). We are also greatly indebted to the CHES Steering Committee for their guidance

and support throughout the process of putting this program together. The peer review process and the production of these proceedings were greatly facilitated by the IACR Webreview System. Shai Halevi (IBM) receives our sincere gratitude for providing and maintaining this software, and for always being prepared to help.

We would also like to acknowledge and thank our sponsors, many of whom have generously supported the workshop over the years. At the time of writing this preface a number of companies had been confirmed as sponsors: Cryptography Research, Inc., CygnaCom Solutions, escrypt GmbH, IBM Research, Oberthur Technologies, Philips Intrinsic-ID, Research Center of Information Security (RCIS) Japan, and Thomson R&D France.

Finally, we would like to thank all the researchers and authors from all over the world who submitted their work to the CHES 2008 conference and whose efforts create the vibrant field of research that CHES is proud to represent.

August 2008

Elisabeth Oswald Pankaj Rohatgi

# **CHES 2008**

Workshop on Cryptographic Hardware and Embedded Systems Washington DC, USA, August 10–13, 2008

Sponsored by the International Association for Cryptologic Research

### General Co-chairs

Kris Gay, George Mason University Jens-Peter Kaps, George Mason University

# **Program Co-chairs**

Elisabeth Oswald, University of Bristol Pankaj Rohatgi, IBM Research

# **Program Committee**

Daniel V. Bailey RSA Laboratories, USA

Lejla Batina Katholieke Universiteit Leuven, Belgium Feng Bao Institute for Infocomm Research, Singapore

Daniel J. Bernstein Univ. of Illinois, Chicago, USA

Suresh Chari IBM Research, USA Christophe Clavier Gemalto, France

Jean-Sebastien Coron University of Luxembourg, Luxembourg

Markus Dichtl Siemens AG, Germany

Louis Goubin Université de Versailles, France Anwar Hasan Univ. of Waterloo, Canada Joshua Jaffe Cryptography Research, USA

Marc Joye Thomson R&D, France

Çetin Kaya KoçOregon State University, USAMarkus KuhnUniversity of Cambridge, UKKlaus KursawePhilips Research, NetherlandsRuby LeePrinceton University, USA

Kerstin Lemke-Rust T-Systems, Germany

Arjen Lenstra EPFL, Switzerland, and Alcatel-Lucent Bell

Laboratories, USA

Stefan Mangard Infineon Technologies, Germany Mitsuru Matsui Mitsubishi Electric, Japan Máaire McLoone Queens University Belfast, UK

### VIII Organization

David Naccache ENS, France Katsuyuki Okeya Hitachi, Japan

Christof Paar Ruhr-Universität Bochum, Germany

Dan Page Univ. of Bristol, UK Pascal Paillier Gemalto, France

Emmanuel Prouff Oberthur Card Systems, France

Jean-Jacques Quisquater Université Catholique de Louvain, Belgium

Anand Raghunathan NEC labs, USA Josyula R. Rao IBM Research, USA

Ahmad-Reza Sadeghi Ruhr-Universität Bochum, Germany

Akashi Satoh AIST, Japan

Erkay Savas Sabanci University, Turkey

Patrick Schaumont Virginia Tech, USA Jean-Pierre Seifert Samsung R&D, USA

Berk Sunar Worcester Polytechnic Institute, USA Masahiko Takenaka Fujitsu Laboratories Ltd, Japan

Kris Tiri Intel, USA Elena Trichina Spansion, France

Ingrid Verbauwhede Katholieke Universiteit Leuven, Belgium

Colin Walter Comodo CA, UK Johannes Wolkerstorfer TU Graz, Austria

# **External Reviewers**

Thomas Eisenbarth Onur Aciicmez Kouichi Itoh Manfred Aigner Takashi Endo Tetsuva Izu Kahraman Akdemir Benoit Feix Charanjit Jutla Toru Akishita Martin Feldhofer Marcelo Kaihara Frédéric Amiel Berndt M. Gammel Jens-Peter Kaps Frederik Armknecht Sergiu Ghetie Anton Kargl Benedikt Gierlichs Muhammad Asim Markus Kasper Guido Bertoni Kevin Gotze Timo Kasper Sumeer Bhola Aline Gouget Chong Hee Kim Ovunc Kocabas Alex Biryukov Rob Granger Masanobu Koike Andrey Bogdanov Vanessa Gratzer Johann Großschädl Konrad Kulikowski Joseph Bonneau Joppe Bos Jorge Guajardo Hans Lähr Arnaud Boscher Shay Gueron T. Lan

Marco Bucci Sylvain Guilley Tanja Lange Tim Güneysu Philippe Bulens Albert Levi Xu Guo David Champagne Yingxi Lu Ghaith Hammouri Zhimin Chen Raimondo Luzzi Benoit Chevallier-Mames Matt Henricksen Francois Macé Emmanuelle Dottax Christoph Herbst Sandra Marcello Saar Drimer Naofumi Homma Mark Marson

Nele Mentens Giacomo de Meulenaer Amir Moradi Shiho Moriai Andrew Moss Michael Naehrig Michael Neve Yasuyuki Nogami Ersin Oksuzoglu Francis Olivier Ahmet Onur Durahim Alina Oprea Berna Ors Toru Owada Erdinc Ozturk Pujan Patel Fabrice Pautot Thomas B. Pedersen

Gilles Piret Thomas Plos Thomas Popp Axel Poschmann Stefan Pyka Matthieu Rivain Francisco Rodriguez-Henriquez Minoru Saeki Ghazanfar A. Safdar Gokay Saldamli Palash Sarkar Vincent Scarlata Dries Schellekens Werner Schindler Jörn-Marc Schmdit Peter Schwabe

Hermann Seuschek

Dave Singelee Boris Skoric Martijn Stam François-Xavier Standaert Daisuke Suzuki Hugues Thiebeault Elena Trichina Toyohiro Tsurumaru Michael Tunstall Pim Tuyls Frédéric Valette Frederik Vercauteren Camille Vuillaume Z. Wang Sung-Ming Yen Huafei Zhu

# **Table of Contents**

| Side-Channel Analysis 1                                                                                   |

|-----------------------------------------------------------------------------------------------------------|

| Attack and Improvement of a Secure S-Box Calculation Based on the Fourier Transform                       |

| Jean-Sébastien Coron, Christophe Giraud, Emmanuel Prouff, and<br>Matthieu Rivain                          |

| Collision-Based Power Analysis of Modular Exponentiation Using Chosen-Message Pairs                       |

| Multiple-Differential Side-Channel Collision Attacks on AES                                               |

| Implementations 1                                                                                         |

| Time-Area Optimized Public-Key Engines: $\mathcal{MQ}$ -Cryptosystems as Replacement for Elliptic Curves? |

| Ultra High Performance ECC over NIST Primes on Commercial FPGAs                                           |

| Exploiting the Power of GPUs for Asymmetric Cryptography                                                  |

| Fault Analysis 1                                                                                          |

| High-Performance Concurrent Error Detection Scheme for AES Hardware                                       |

| A Lightweight Concurrent Fault Detection Scheme for the AES S-Boxes Using Normal Basis                    |

| RSA with CRT: A New Cost-Effective Solution to Thwart Fault  Attacks                                      |

| Random Number Generation                                                                                                               |     |

|----------------------------------------------------------------------------------------------------------------------------------------|-----|

| A Design for a Physical RNG with Robust Entropy Estimators                                                                             | 146 |

| Fast Digital TRNG Based on Metastable Ring Oscillator                                                                                  | 164 |

| Efficient Helper Data Key Extractor on FPGAs                                                                                           | 181 |

| Side-Channel Analysis 2                                                                                                                |     |

| The Carry Leakage on the Randomized Exponent Countermeasure<br>Pierre-Alain Fouque, Denis Réal, Frédéric Valette, and<br>Mhamed Drissi | 198 |

| Recovering Secret Keys from Weak Side Channel Traces of Differing Lengths  Colin D. Walter                                             | 214 |

| Attacking State-of-the-Art Software Countermeasures—A Case Study for AES                                                               | 228 |

| Cryptography and Cryptanalysis                                                                                                         |     |

| Binary Edwards Curves                                                                                                                  | 244 |

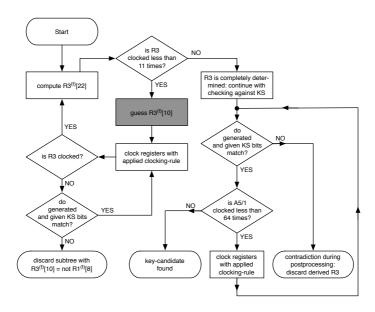

| A Real-World Attack Breaking A5/1 within Hours                                                                                         | 266 |

| Hash Functions and RFID Tags: Mind the Gap                                                                                             | 283 |

| Implementations 2                                                                                                                      |     |

| A New Bit-Serial Architecture for Field Multiplication Using Polynomial Bases                                                          | 300 |

| A Very Compact Hardware Implementation of the MISTY1 Block                                                                             | 915 |

| Cipher  Dai Yamamoto, Jun Yajima, and Kouichi Itoh                                                                                     | 315 |

| Table of Contents                                                                                                                | XIII |

|----------------------------------------------------------------------------------------------------------------------------------|------|

| Light-Weight Instruction Set Extensions for Bit-Sliced Cryptography<br>Philipp Grabher, Johann Großschädl, and Dan Page          | 331  |

| Fault Analysis 2                                                                                                                 |      |

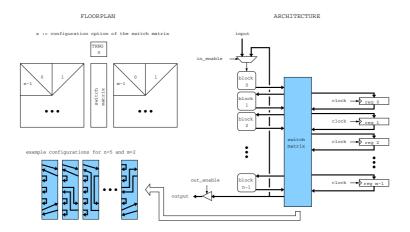

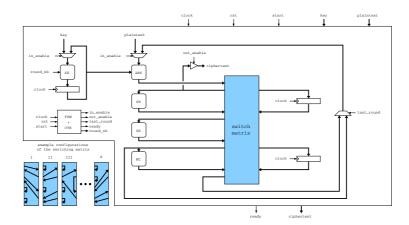

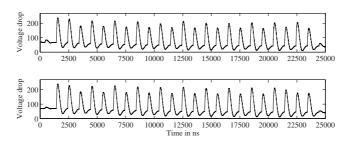

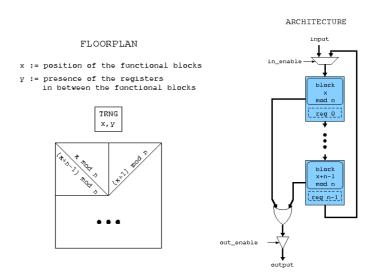

| Power and Fault Analysis Resistance in Hardware through Dynamic Reconfiguration                                                  | 346  |

| RFID and Its Vulnerability to Faults                                                                                             | 363  |

| Perturbating RSA Public Keys: An Improved Attack                                                                                 | 380  |

| Side-Channel Analysis 3                                                                                                          |      |

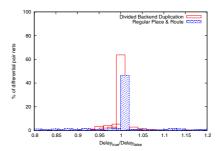

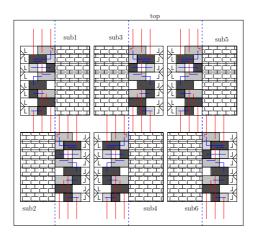

| Divided Backend Duplication Methodology for Balanced Dual Rail Routing                                                           | 396  |

| Using Subspace-Based Template Attacks to Compare and Combine Power and Electromagnetic Information Leakages                      | 411  |

| Mutual Information Analysis: A Generic Side-Channel Distinguisher  Benedikt Gierlichs, Lejla Batina, Pim Tuyls, and Bart Preneel | 426  |

| Invited Talks                                                                                                                    |      |

| RSA—Past, Present, Future                                                                                                        | 443  |

| A Vision for Platform Security  Ernie Brickell                                                                                   | 444  |

| Author Index                                                                                                                     | 445  |

# Attack and Improvement of a Secure S-Box Calculation Based on the Fourier Transform

Jean-Sébastien Coron<sup>1</sup>, Christophe Giraud<sup>2</sup>, Emmanuel Prouff<sup>2</sup>, and Matthieu Rivain<sup>1,2</sup>

**Abstract.** At CHES 2006, a DPA countermeasure based on the Fourier Transform was published. This generic countermeasure aims at protecting from DPA any S-box calculation used in symmetric cryptosystems implementations. In this paper, we show that this countermeasure has a flaw and that it can be broken by first order DPA. Moreover, we have successfully put into practice our attack on two different S-box implementations. Finally, we propose an improvement of the original countermeasure and we prove its security against first order DPA.

# 1 Introduction

The processing of a cryptographic algorithm on a physical device may leak information about the manipulated data. To exploit this information, Side Channel Attacks (SCA) were introduced in 1996, cf. [8]. It is today composed of a large variety of attacks that differ in the attack model, the nature of the side channels they target or the leakage treatments they perform. The Differential Power Analysis (DPA) introduced in [9] is probably the one which has received the most attention in the literature. This attack has indeed been demonstrated to be very powerful against unprotected cryptographic implementations, where it allows the attacker to recover the value of a secret key with only a few leakage measurements. Roughly speaking, a DPA is a statistical attack that correlates a physical leakage with the values of particular intermediate variables (called sensitive variables in this paper) that depend on both a public value and the secret key. To avoid information leakage and its exploitation by DPA, the manipulation of sensitive variables must be protected by adding countermeasures to the algorithm.

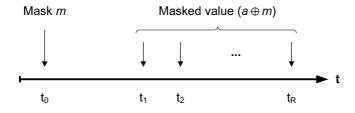

A very common countermeasure to protect block cipher implementations from DPA is to mask every sensitive variable with a randomly generated variable (called *mask*) and then to perform the calculations by only manipulating the masked variable and/or the mask. When such a technique is applied, a problem occurs which is usually referred in the literature as the *mask correction Problem*. It relies on the difficulty of masking the calculation of non-linear sub-functions (*e.g.* the so-called *S-boxes*), without ever manipulating an intermediate variable that depends on sensitive data. Many papers have been published that aim at providing a solution to this problem (see for instance [1,7,10,11,12]). At CHES

E. Oswald and P. Rohatgi (Eds.): CHES 2008, LNCS 5154, pp. 1–14, 2008.

<sup>©</sup> International Association for Cryptologic Research 2008

2006, Prouff, Giraud and Aumônier proposed in [11] a solution that may be of particular interest when the input/output dimensions of the function to protect are small and when the masks values are regenerated many times during the algorithm processing. Moreover, the solution is provided together with a proof of security that allows the reader to formally validate its security. In this paper, we show that contrary to what is claimed in [11], a DPA attack can be successfully mounted against this countermeasure. We exhibit the flaw upon which our attack is based and we present how to successfully exploit it to recover the value of a secret parameter. Finally, we propose an improvement of the countermeasure proposed in [11] and we prove its security versus DPA in a realistic model.

# 2 Preliminaries

In the rest of the paper, we say that a variable is sensitive with respect to DPA (shortened to sensitive variable in the context of the present paper) if it is a non-constant function of a plaintext and a secret key. A DPA (also called first order DPA in the literature when it is compared to higher order DPA) exploits the leakage about a single intermediate sensitive variable. Hereafter, we recall the formal definition of the security against DPA (see for instance [2,4,11]).

**Definition 1.** A cryptographic algorithm is said to be secure against DPA if all its intermediate variables are independent of any sensitive variable.

Conversely, an algorithm is said to admit a *first order flaw* if one of its intermediate variables depends on a sensitive variable.

A common countermeasure against DPA is to add (by bitwise or modular addition) a random value called the *mask* to each sensitive variable. Masks and masked variables propagate throughout the cipher in such a way that every intermediate variable is independent of any sensitive variable. This strategy, called *first order masking*, ensures that the instantaneous leakage is independent of any sensitive variable, thus rendering DPA ineffective.

As pointed out for instance in [6,1], the tricky part when masking the implementation of an algorithm is to deal with the following problem, called *mask* correction Problem:

Problem 1. Let F be a (n,m)-function (that is a function from  $\mathbb{F}_2^n$  into  $\mathbb{F}_2^m$ ). From a masked input  $Z \oplus R_1 \in \mathbb{F}_2^n$ , the mask  $R_1 \in \mathbb{F}_2^n$  and an output mask  $R_2 \in \mathbb{F}_2^m$ , compute  $F(Z) \oplus R_2$  without introducing any first order flaw.

# 3 Secure S-Box Calculation Based on the Fourier Transform

In [11], an algorithm claimed to solve Problem 1 is proposed. The method is based on the involutivity property of the *Fourier Transform*. Before describing it, let us first recall some basics about the transformation itself.

Algorithm 1. Computation of an arithmetically masked S-box output from a boolean masked input

INPUTS: A masked input  $\tilde{Z} = Z \oplus R_1$ , the input mask  $R_1$  and a lookup table  $\hat{F}$ OUTPUT: The 3-tuple  $((-1)^{(\tilde{Z}\oplus R_2)\cdot R_1}F(Z)+R_3 \mod 2^n,R_3,R_2)$  where  $R_2$  and  $R_3$  are random values.

- 1. Pick up three *n*-bit randoms  $R_2$ ,  $R_3$  and  $R_4$

- 2.  $result \leftarrow 2^n R_3 + R_4$

- 3. for a from 0 to  $2^n 1$  do

4.

$$T_1 \leftarrow \text{SSP}(a, \widetilde{Z})$$

$[T_1 = (-1)^{a \cdot \widetilde{Z}}]$

5.

$$T_2 \leftarrow \widetilde{Z} \oplus a$$

$[T_2 = \widetilde{Z} \oplus a]$

6.

$$T_2 \leftarrow T_2 \oplus R_2$$

$[T_2 = \widetilde{Z} \oplus a \oplus R_2]$

7.

$$T_2 \leftarrow \text{SSP}(R_1, T_2)$$

$$[T_2 = (-1)^{R_1 \cdot (\tilde{Z} \oplus a \oplus R_2)}]$$

8.  $T_2 \leftarrow T_1 \times T_2$

$$[T_2 = (-1)^{a \cdot \tilde{Z} \oplus R_1 \cdot (\tilde{Z} \oplus a \oplus R_2)}]$$

8.

$$T_2 \leftarrow T_1 \times T_2$$

$$[T_2 = (-1)^{a \cdot Z \oplus R_1 \cdot (Z \oplus a \oplus R_2)}]$$

9.

$$T_2 \leftarrow T_2 \times \widehat{F}(a)$$

$$[T_2 = \widehat{F}(a)(-1)^{a \cdot \widehat{Z} \oplus R_1 \cdot (\widehat{Z} \oplus a \oplus R_2)}]$$

- $[T_2 = \widehat{F}(a)(-1)^{a \cdot \widetilde{Z} \oplus R_1 \cdot (\widetilde{Z} \oplus a \oplus R_2)}]$   $[result = (2^n R_3 + R_4) \boxplus \sum_{i \in \{0, a\}} \widehat{F}(i)(-1)^{i \cdot \widetilde{Z} \oplus R_1 \cdot (\widetilde{Z} \oplus i \oplus R_2)}]$  $result \leftarrow result \boxplus T_2$ 10.

- 11. end

- $[result = (-1)^{(\tilde{Z} \oplus R_2) \cdot R_1} F(Z) + R_3 \mod 2^n]$ 12.  $result \leftarrow result \gg n$

- 13. return  $(result, R_3, R_2)$

For every (n, m)-function F, the Fourier transform  $\widehat{F}$  of F is defined for every  $Z=(Z_0,\cdots,Z_{n-1})\in\mathbb{F}_2^n$  by:

$$\widehat{F}(Z) = \sum_{a \in \mathbb{F}_n^n} F(a)(-1)^{a \cdot Z} , \qquad (1)$$

where  $\cdot$  denotes the scalar product defined by  $a \cdot Z = \bigoplus_{i=0}^{n-1} a_i Z_i$ .

It is well known that this transformation is involutive, which means that  $\widehat{\widehat{F}} = 2^n F$  or equivalently that:

$$F(Z) = \frac{1}{2^n} \sum_{a \in \mathbb{F}_2^n} \widehat{F}(a) (-1)^{a \cdot Z}, \ Z \in \mathbb{F}_2^n \ . \tag{2}$$

Let  $R_1, R_2, R_3$  and  $R_4$  be 4 random masks belonging to  $\mathbb{F}_2^n$ , and let Z denotes a sensitive variable. The algorithm proposed in [11] to process  $F(Z)+R_3 \mod 2^n$ securely from  $Z = Z \oplus R_1$  and  $R_1$ , implements the right-hand side calculus of the following relation (which is a slightly modified version of Relation (2)):

$$(-1)^{(\widetilde{Z} \oplus R_2) \cdot R_1} F(Z) + R_3 \mod 2^n$$

$$= \left\lfloor \frac{1}{2^n} \left( R' + \sum_{a \in \mathbb{F}_2^n} \widehat{F}(a) (-1)^{a \cdot \widetilde{Z} \oplus R_1 \cdot (\widetilde{Z} \oplus a \oplus R_2)} \mod 2^{2n} \right) \right\rfloor , \quad (3)$$

where  $R' = 2^n R_3 + R_4$ .

Let SSP denote the signed scalar product  $X, Y \mapsto (-1)^{X \cdot Y}$ , let  $\boxplus$  denote the addition modulo  $2^{2n}$  and let  $\times$  denote the multiplication of two values belonging to  $\{-1,1\}$ . We recall hereafter the algorithm proposed in [11] to process the right-hand side of (3) securely.

Finally, it is proposed in [11] to use the method described in [5] in order to transform the arithmetic masking of the output of Algorithm 1 into a boolean masking.

The authors of [11] had proposed a proof of security *versus* DPA for the countermeasure defined by Algorithm 1, but as we will see in the next section, the proof is flawed and the countermeasure is not secure against DPA.

# 4 DPA against the Fourier Transform Based S-Box Calculation

### 4.1 First Order Flaw

Unlike what is claimed in [11], the implementation of Algorithm 1 is not immune against DPA. Indeed, the variable  $V = a \cdot \widetilde{Z} \oplus R_1 \cdot (\widetilde{Z} \oplus a \oplus R_2)$  processed at Step 8 brings information about the sensitive variable Z (recalling  $\widetilde{Z} = Z \oplus R_1$ ). To exhibit the dependency between V and Z, let us first rewrite V as follows:

$$V = a \cdot \widetilde{Z} \oplus R_1 \cdot (\widetilde{Z} \oplus a \oplus R_2)$$

=  $a \cdot (Z \oplus R_1) \oplus R_1 \cdot (\widetilde{Z} \oplus a \oplus R_2)$

=  $a \cdot Z \oplus R_1 \cdot (\widetilde{Z} \oplus R_2)$ .

The relation above shows that the intermediate variable V equals the sensitive variable  $a \cdot Z$  (a being a loop index) masked with the scalar product  $R_1 \cdot (\widetilde{Z} \oplus R_2)$ . Since  $R_2$  is uniformly distributed and is independent of both Z and  $R_1$ , then so does the variable  $\widetilde{Z} \oplus R_2$ . The flaw of the method proposed in [11] comes from the fact that the scalar product of two uniformly distributed random variables does not output an uniformly distributed random variable. For example, the product  $b_1 \cdot b_2$  of two random bits  $b_1$  and  $b_2$  equals 0 with probability 3/4, and equals 1 with probability 1/4. More generally, for n-bit random variables we have the following lemma.

**Lemma 1.** Let X and Y be two random variables uniformly distributed over  $\mathbb{F}_2^n$  and mutually independent. Then the scalar product  $X \cdot Y$  satisfies

$$\Pr[X \cdot Y = 0] = \frac{1}{2} + \frac{1}{2^{n+1}} \ . \tag{4}$$

*Proof.* We have:

$$P[X \cdot Y = 0] = P[X \neq 0] \cdot P[X \cdot Y = 0 | X \neq 0] + P[X = 0] \cdot P[X \cdot Y = 0 | X = 0] \;.$$

Since the Boolean function  $y \in \mathbb{F}_2^n \mapsto x \cdot y$  is linear and not null for every  $x \neq 0$ , we have  $\#\{x \cdot y = 1\} = \#\{x \cdot y = 0\} = 2^{n-1}$ . This, together with the fact that X and Y are independent, implies  $P[X \cdot Y = 0 | X \neq 0] = \frac{1}{2}$ . Since  $P[X \cdot Y = 0 | X = 0] = 1$  and  $P[X \neq 0] = \frac{2^n - 1}{2^n}$ , we deduce (4).

Remark 1. In the security proof conducted in [11], it is stated that the uniform distribution of X and Y implies the one of  $X \cdot Y$ . We show in Lemma 1 that this assertion is actually wrong.

Lemma 1 implies that the distribution of  $R_1 \cdot (\widetilde{Z} \oplus R_2)$  has a bias  $\frac{1}{2^{n+1}}$  with respect to the uniform distribution. Since the sensitive variable  $a \cdot Z$  is masked with a biased mask, the variable V defined in (4) leaks information on  $a \cdot Z$ . This information can be used to recover Z by DPA.

### 4.2 DPA Attack

A DPA attack [9] targets the leakage L(b) generated by the processing of a sensitive bit b in order to recover information about a secret which we denote here by  $k^*$ . It can be performed with only a few information about the leakage and it actually only assumes that the expectation of L(b) depends on the value of b. Let us first recall the outlines of the attack in the general case where b can be expressed as:

$$b = f(X, k^*) , (5)$$

where f is a Boolean function and X is a public variable.

**Description.** To perform a DPA, the target algorithm is executed several times, say N, for a sequence of values  $(x_i)_{i\leq N}$  taken by X. For each execution, the attacker measures the leakage  $l_i$  generated by the processing of b. Then, the resulting leakage measurement sequence  $(l_i)_{i\leq N}$  is involved to (in)validate a key hypothesis k on  $k^*$ . For such a purpose, the attacker first computes the sequence of guesses  $(b_i)_{i\leq N}$  which are the predicted values of the bit b processed in the successive executions: namely, for every  $i\leq N$  we have  $b_i=f(x_i,k)$ . Then, the leakage measurements are separated in two categories: the ones for which the predicted bit  $b_i$  is equal to 1, and the ones for which it is equal to 0. Finally, the so-called differential  $\Delta_k$  corresponding to the difference between the mean values of the two sets is computed:

$$\Delta_k = \frac{\sum_{i=1}^N b_i \times l_i}{\sum_{i=1}^N b_i} - \frac{\sum_{i=1}^N (1 - b_i) \times l_i}{\sum_{i=1}^N (1 - b_i)} . \tag{6}$$

If the key hypothesis is correct then the expectation satisfies:

$$E[\Delta_{k^*}] = E[L(1)] - E[L(0)]. \tag{7}$$

If the key hypothesis is incorrect then a ratio  $\alpha \in [0, 1]$  of the  $b_i$ 's is wrongly predicted and the expectation of the differential satisfies:

$$E[\Delta_k] = (1 - 2\alpha) (E[L(1)] - E[L(0)]).$$

(8)

Since  $\alpha$  is usually around  $\frac{1}{2}$ , we have  $E[\Delta_{k\neq k^*}] \simeq 0$ . This implies that, for a sufficiently large N, the correct key hypothesis is such that  $\Delta_k$  is of maximum amplitude.

Remark 2. Depending on the function f, it may happen that the correct key hypothesis is not the single one for which  $\Delta_k$  is of maximum amplitude. Indeed, a key hypothesis such that  $\alpha=1$  also results in a differential of maximal amplitude. According to (6), this differential and the one corresponding to the correct key hypothesis have exactly the same amplitude but have opposite signs. To differentiate them the attacker needs to determine the polarity of E[L(1)] - E[L(0)].

**DPA Attack Exploiting a Biased Mask.** Let us now consider the case where the target bit b is masked, namely:

$$b = f(X, k^*) \oplus R , \qquad (9)$$

where R is a random bit.

If R is uniformly distributed over  $\mathbb{F}_2$ , then no successful DPA attack is possible. Indeed, in that case b equals 0  $(resp.\ 1)$  with probability  $\frac{1}{2}$  independently of  $k^*$ . Conversely, when the distribution of R is biased compared to the uniform distribution, then the distribution of b depends on  $f(X, k^*)$ , which renders DPA possible. In the following, we denote by  $\varepsilon \neq 0$  the bias such that  $P[R=0] = \frac{1}{2} + \varepsilon$ .

The DPA works in the same way as in the unmasked case. The sequence of guesses is still defined as  $b_i = f(x_i, k)$  (since R is not predictable) and the differential  $\Delta_k$  is computed according to (6). The randomization provided by R implies that the bit effectively processed equals  $f(x_i, k^*)$  with probability  $\frac{1}{2} + \varepsilon$ . One deduces that, for the correct key hypothesis, a portion  $\frac{1}{2} + \varepsilon$  of the  $b_i$ 's is correctly predicted while a portion  $\frac{1}{2} - \varepsilon$  is wrongly predicted in average. This implies that the expectation of the differential for the correct key hypothesis satisfies:

$$E[\varDelta_{k^\star}] = \left(\frac{1}{2} + \varepsilon\right) \left( E[L(1)] - E[L(0)] \right) + \left(\frac{1}{2} - \varepsilon\right) \left( E[L(0)] - E[L(1)] \right) \ ,$$

that is:

$$E[\Delta_{k^*}] = 2\varepsilon \times (E[L(1)] - E[L(0)]).$$

Hence the expectation of  $\Delta_{k^*}$  is divided by a factor  $\frac{1}{2\varepsilon}$  compared to an unprotected implementation (this also holds for the differentials  $\Delta_k$  obtained for wrong key hypotheses – see Appendix A – ). This implies, according to the analysis in [3], that the number of required leakage measurements is roughly multiplied by  $(\frac{1}{2\varepsilon})^2$ . A more detailed analysis is conducted in Appendix A where we give the exact distribution of  $\Delta_k$ , assuming that the leakage noise has a Gaussian distribution.

As a result, Lemma 1 implies that a DPA on Algorithm 1 exploiting the flaw exhibited in Section 4.1 is expected to require about  $2^{2n}$  times more leakage measurements than a DPA when no masking is used. Since Algorithm 1 is only interesting for a small value of n (e.g. n = 4), this factor is not prohibitive.

### 4.3 DPA Attack on the Flaw

In this section, we apply the DPA attack described in Section 4.2 in order to exploit the flaw exhibited in Section 4.1. More precisely, our attack targets a bit

b which is a scalar product  $a \cdot Z$  masked with a biased mask  $R = R_1 \cdot (\tilde{Z} \oplus R_2)$ , that is

$$b = a \cdot Z \oplus R \ . \tag{10}$$

We recall that a refers to a loop index in Algorithm 1 and that its value can be chosen by the attacker among  $\{0, \dots, 2^n - 1\}$ . The sensitive variable Z is the sensitive S-box input and it can be written as a function of a public variable X and a piece of secret data  $k^*$ . The way our attack is performed depends on this function which can take several forms. In the sequel we consider two usual cases.

The first one is referred as the *linear case* and assumes:

$$Z = X \oplus k^*$$

.

This occurs for instance in AES and in FOX algorithms for the first round S-box calculation.

The second case, referred as the *non-linear case*, assumes the existence of a non-linear transformation  $\phi$  such that:

$$Z = \phi(X \oplus k^*)$$

.

This occurs for instance in the AES algorithm implemented using the *composite* field method [10,11] (see [11, §4.1] for details). In that case,  $\phi$  is the non-linear (8,4)-function which from  $a \in \mathbb{F}_{256}$  processes  $d \in \mathbb{F}_{16}$  according to the notations of [10,11].

The Linear Case. We consider here the case where the targeted bit can be expressed as  $b = a \cdot (X \oplus k^*) \oplus R$  that is:

$$b = a \cdot X \oplus a \cdot k^* \oplus R . \tag{11}$$

The bit b in (11) only depends on one secret binary value  $a \cdot k^*$ . Therefore, a DPA on b will provide at most one bit of information on  $k^*$ . Hence, recovering the whole secret  $k^*$  requires to perform a DPA attack on b for t different loop indices  $a_0, ..., a_{t-1}$ .

When mounting a DPA attack on b for a particular loop index a, the sequence of guesses can only take one of the two following forms:  $(a \cdot x_i)_i$  or  $(a \cdot x_i \oplus 1)_i$ . According to (6), these two sequences result in two differentials that are opposite one to each other. The attacker does not know a priori which of these differentials correspond to the correct key hypothesis. Indeed, depending on the device, the polarity  $(-1)^s$  of the good differential  $\Delta_{a \cdot k^*}$  may be positive or negative. In other terms, the DPA allows the attacker to recover the value of  $a \cdot k^* \oplus s$ , where  $k^*$  and s are unknown.

Since the polarity s is the same for all the loop indices a, then performing t DPA attacks for t different loop indices  $a_0, ..., a_{t-1}$  provides the attacker with a system of t equations and n+1 variables (the polarity bit s and the n bits of  $k^*$ ). Solving this system requires to have at least t=n+1 equations. After choosing n indices  $a_i$  having linearly independent vectorial representations in  $\mathbb{F}_2^n$  and after defining  $a_n = a_0 \oplus a_1$ , it can be checked that solving the system allows the attacker to unambiguously determine the value of  $k^*$ .

The Non-linear Case. We now consider the case where b satisfies:

$$b = a \cdot \phi(X \oplus k^*) \oplus R \ . \tag{12}$$

For a non-linear  $\phi$ , the attack is analogous to a classical DPA on some output bit of e.g. a DES or AES S-box [9]. The non-linearity of  $\phi$  ensures that for the correct key hypotheses a peak of maximal amplitude will appear while for most other key hypothesis no peak will appear. This enables to fully recover  $k^*$ .

In this section, we have described how to exploit the leakage on a sensitive bit which is masked with a biased random bit. In the linear case, the attack requires to perform n+1 DPAs while only one DPA is needed in the non-linear case. In the following section, we present experimental results for these two attacks.

# 5 Experimental Results

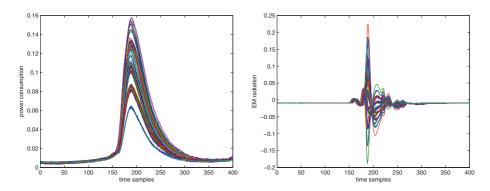

We put into practice the attacks described in Section 4.2 for two S-box implementations on an 8-bit smart card. Both attacks exploited the power consumption resulting from several S-box calculations.

Regarding the linear case, we performed the attack on the S-box calculation of FOX algorithm during the first round protected by the method described in [11]. In this case, the sensitive bits we targeted are of the form  $a \cdot (X \oplus k^*) \oplus R$ , where  $a, X, k^* \in \mathbb{F}_2^4$ . Following the outlines of the attack described in Section 4.3 for the linear case, we have applied 4+1 DPAs on five different loop iterations of Algorithm 1, namely one DPA for every  $a \in \{1, 2, 4, 8, 3\}$ .

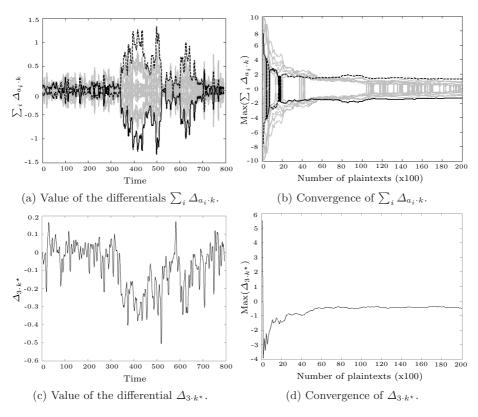

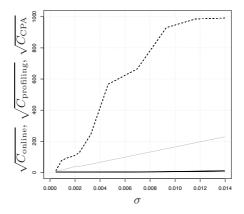

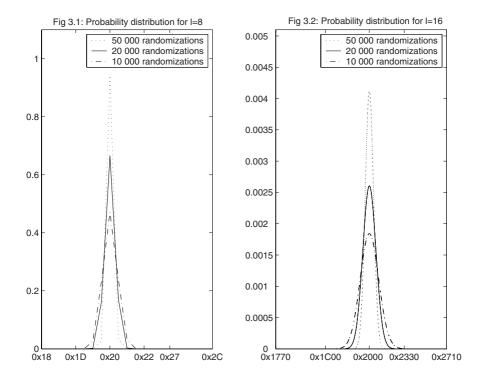

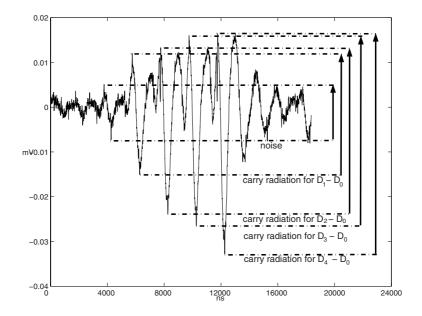

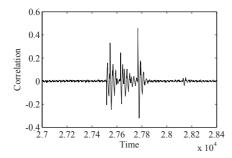

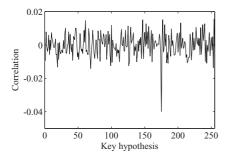

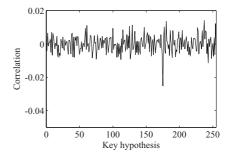

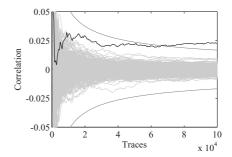

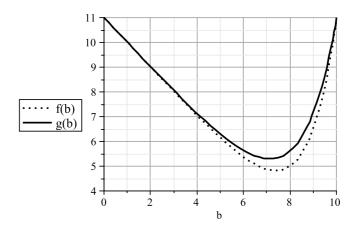

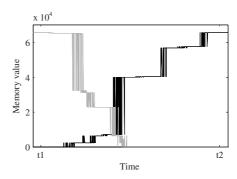

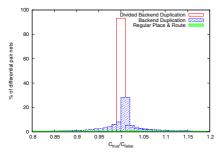

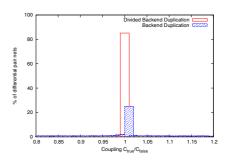

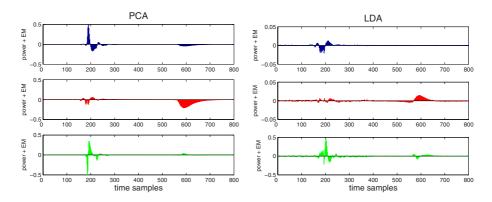

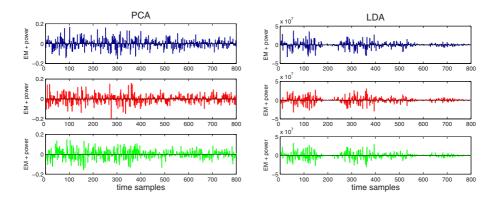

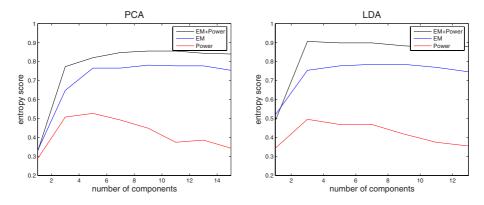

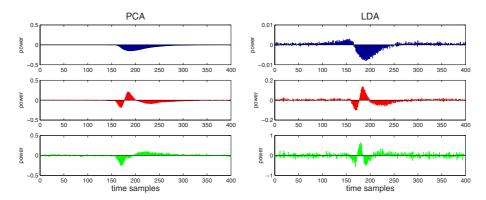

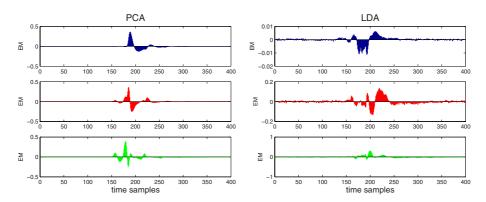

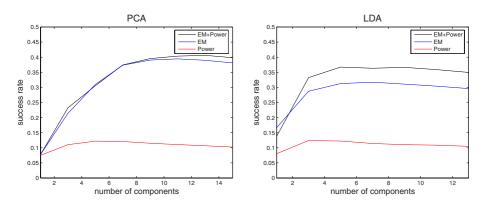

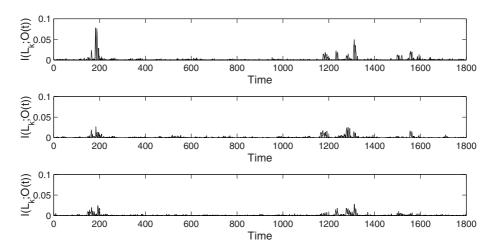

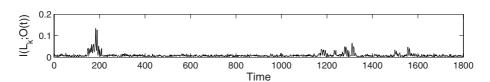

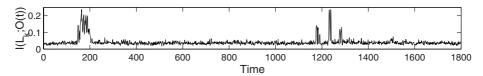

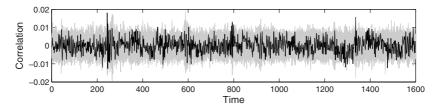

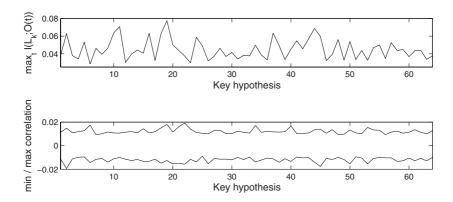

Figure 1.a represents the value of  $\sum_{i=0}^{3} \Delta_{a_i \cdot k}$ , where  $a_i = 2^i$ , obtained after 20 000 executions of the algorithm. The full black curve corresponds to the correct subkey value  $k^*$  and the dotted black curve corresponds to the complementary of this value. As expected, these two candidates are such that the highest peaks of the differential vectors  $\Delta_{a_i \cdot k}$  are either all positive or all negative, hence leading to the highest amplitudes for  $\sum_{i=0}^{3} \Delta_{a_i \cdot k}$ . As explained in Section 4.3, we then computed the differential  $\Delta_{a \cdot k^*}$  for  $a = a_0 \oplus a_1 = 3$ . Figure 1.c illustrates this computation. The polarity of the highest peak of  $\Delta_{3 \cdot k^*}$  being negative, one deduces that the correct subkey value  $k^*$  corresponds to the full black curve in Figure 1.a.

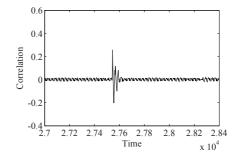

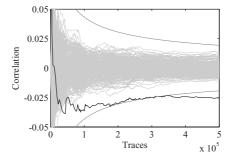

Figures 1.b and 1.d represent respectively the convergence of the peak of maximal amplitude for  $\sum_{i=0}^{3} \Delta_{a_i \cdot k}$  and for  $\Delta_{3 \cdot k^*}$  according to the number of power consumption measurements. By analyzing these curves, we deduce that the value of the 4-bit subkey  $k^*$  is recovered by using about 8 000 executions of the algorithm.

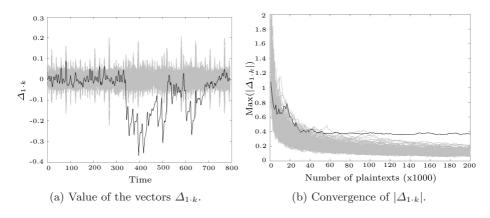

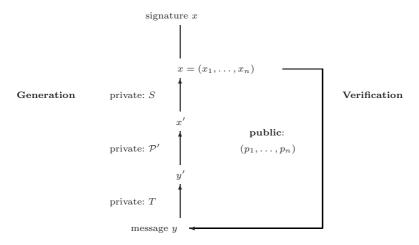

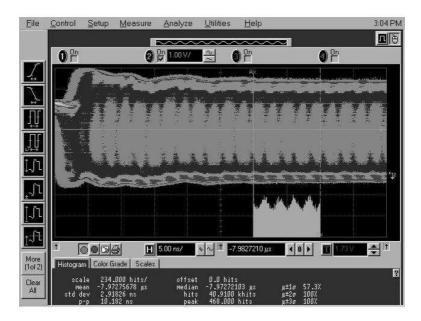

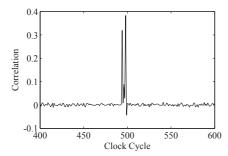

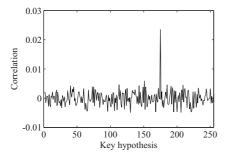

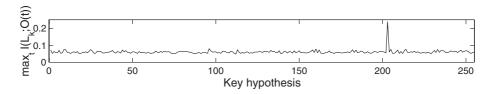

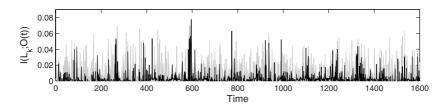

Regarding the non-linear case, we attacked the AES S-box calculation using the composite field method in order to perform the inversion in  $\mathbb{F}_2^4$  instead of  $\mathbb{F}_2^8$  and the method of [11] to protect this inversion (see [11, § 4.1] for more details). In that case, the targeted bit is of the form  $a \cdot \phi(X \oplus k^*) \oplus R$  where  $X, k^* \in \mathbb{F}_2^8$ ,  $a \in \mathbb{F}_2^4$  and  $\phi : \mathbb{F}_2^8 \to \mathbb{F}_2^4$ . Figure 2.a represents the value of the differentials  $\Delta_k$ 's for  $k \in \mathbb{F}_2^8$  and a = 1, when 200 000 executions of the algorithm are used. It can be seen that the correct subkey  $k^*$  (plotted in black) is easily distinguishable.

Fig. 1. Practical DPA attack – the linear case

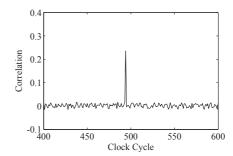

Figure 2.b represents the convergence of the maximum peak amplitude for the differentials according to the number of power consumption measurements. The analysis of these curves shows us that the value of the 8-bit subkey  $k^*$  is recovered after about 100 000 executions of the algorithm.

# 6 An Improved Version of a Secure S-Box Calculation

In the following we propose an improvement of Algorithm 1 that allows to circumvent the flaw depicted in Section 4.1 and also leads to a more efficient implementation.

The new algorithm is still a secure calculation of a Fourier Transform but it is based on a slightly modified version of (3) which we rewrite in the following form:

$$(-1)^{R_2} F(Z) + R_3 \mod 2^n$$

$$= \left[ \frac{1}{2^n} \left( R' + \sum_{a \in \mathbb{F}_2^n} \widehat{F}(a) (-1)^{R_2 \oplus a \cdot \widetilde{Z} \oplus a \cdot R_1} \mod 2^{2n} \right) \right] , \quad (13)$$

where  $\widetilde{Z} = Z \oplus R_1$ ,  $R_2 \in \mathbb{F}_2$ ,  $(R_1, R_3, R_4) \in (\mathbb{F}_2^n)^3$  and  $R' = 2^n R_3 + R_4$ .

Fig. 2. Practical DPA attack – the non-linear case

After a brief look at (13) (and before the deeper analysis conducted later on in this section), we can notice that the sensitive variable  $a \cdot Z$  is now masked with the uniformly distributed random bit  $R_2$ . Furthermore, it may be noticed that the exponent in the summation in (13) involves less operations than in (3).

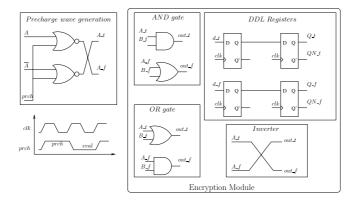

Let us denote by SP the function  $X, Y \mapsto X \cdot Y$  and by SFT the function  $X, T \mapsto \widehat{F}(X)(-1)^T$ . As we prove in this section, Algorithm 2 implements (13) securely.

```

INPUTS: A masked value \tilde{Z} = Z \oplus R_1 and the mask R_1 OUTPUT: The 3-tuple ((-1)^{R_2}F(Z) + R_3 \mod 2^n, R_3, R_2), where R_2 and R_3 are random values.

```

Algorithm 2. First order Secure S-box calculation

```

1. Generate a random bit R_2

2. Generate two n-bit random R_3 and R_4

3. result \leftarrow 2^n R_3 + R_4

4. for a from 0 to 2^n - 1 do

T_1 \leftarrow \mathrm{SP}(a, \widetilde{Z})

[T_1 = a \cdot \widetilde{Z}]

T_1 \leftarrow T_1 \oplus R_2

[T_1 = R_2 \oplus a \cdot \widetilde{Z}]

6.

[T_2 = a \cdot R_1]

T_2 \leftarrow \mathrm{SP}(a, R_1)

[T = R \oplus a \cdot Z]

T \leftarrow T \oplus T

8.

[T_1 = \widehat{F}(a)(-1)^{R_2 \oplus a \cdot Z}]

T_1 \leftarrow \text{SFT}(a, T_1)

9.

[result = (2^n R_3 + R_4) \boxplus \sum_{i \in \{0,a\}} \widehat{F}(i) (-1)^{R_2 \oplus i \cdot Z}]

10.

result \leftarrow result \boxplus T_1

11. end

[result = (-1)^{R_2}F(Z) + R_3 \mod 2^n]

12. result \leftarrow result \gg n

13. return (result, R_3, R_2)

```

Efficiency Analysis. Although Algorithm 2 is more secure than Algorithm 1, it is also faster. For each loop, Algorithm 2 requires two XORs, two calls to the function SP and one call to the lookup table SFT. Therefore, for each loop Algorithm 1 performs 2 extra multiplications compared to Algorithm 2. Combining

this result with the fact that function SP is slightly faster than function SSP, we deduce that our method is faster than the one proposed in [11].

**Security Analysis.** In Table 1, we list the intermediate variables of Algorithm 1 that involve a sensitive variable. The values which only depend on the loop counter or on a random value are obviously omitted.

| Step | Ir       | strı         | action                 | Masked Value                                                                 | Mask(s)                  |

|------|----------|--------------|------------------------|------------------------------------------------------------------------------|--------------------------|

| 5.1  | register | · -          | $\widetilde{Z}$        | $\widetilde{Z}$                                                              | $R_1$                    |

| 5.2  | $T_1$    | $\leftarrow$ | $SP(a, \widetilde{Z})$ | $a\cdot\widetilde{Z}$                                                        | $a \cdot R_1$            |

| 6    | $T_1$    | $\leftarrow$ | $T_1 \oplus R_2$       | $R_2 \oplus a \cdot \widetilde{Z}$                                           | $R_2 \oplus a \cdot R_1$ |

| 8    | $T_1$    | $\leftarrow$ | $T_1 \oplus T_2$       | $R_2 \oplus a \cdot Z$                                                       | $R_2$                    |

| 9    | $T_1$    | $\leftarrow$ | $SFT(a, T_1)$          | $\widehat{F}(a)(-1)^{R_2 \oplus a \cdot Z}$                                  | $R_2$                    |

| 10   | result   | $\leftarrow$ | $result \boxplus T_1$  | $(2^n R_3 + R_4) \boxplus \sum_i \widehat{F}(i) (-1)^{R_2 \oplus i \cdot Z}$ | $(R_2, R_3, R_4)$        |

| 11   | result   | $\leftarrow$ | $result \gg n$         | $(-1)^{R_2}F(Z) + R_3 \bmod 2^n$                                             | $R_3$                    |

**Table 1.** The different sensitive values manipulated during Algorithm 2

As it can be checked in Table 1, the intermediate variables manipulated at Steps 5.1, 6, 8, 9, 10 and 11 are additively masked with a uniformly distributed random variable (resp.  $R_1$ ,  $R_2 \oplus a \cdot R_1$ ,  $R_2$ ,  $R_2$ ,  $R_3 || R_4$  and  $R_3$ ) which is independent of the sensitive variable. Those intermediate variables are therefore independent of the sensitive variable Z.

The intermediate variable at Step 5.2 can be rewritten  $a \cdot Z \oplus a \cdot R_1$ . When a equals 0, this variable equals 0 whatever Z and  $R_1$ . Otherwise, for every  $a \neq 0$  the variable  $a \cdot R_1$  is uniformly distributed and independent of Z. We deduce that  $a \cdot Z \oplus a \cdot R_1$  (and hence  $a \cdot \widetilde{Z}$ ) is independent of Z whatever a.

Therefore, we have proved that all the intermediate variables manipulated during the execution of Algorithm 1 are independent of Z, which implies that our method is secure against first order DPA.

# 7 Conclusion

In this paper, we have shown that a provably secure DPA countermeasure published at CHES 2006 has a flaw. We have explained how this flaw can be exploited to mount an efficient attack on S-box implementations protected by this countermeasure. Our attack is not only theoretical since we have successfully put it into practice on two different S-box implementations: the AES S-box using the composite field method and the FOX S-box.

Finally, we have proposed an improvement of the CHES 2006 countermeasure for which we prove the resistance against first order DPA. Moreover we showed that our improvement is not only more secure but can also be implemented more efficiently than the original countermeasure.

# References

- 1. Akkar, M.-L., Giraud, C.: An Implementation of DES and AES, Secure against Some Attacks. In: Koç, Ç.K., Naccache, D., Paar, C. (eds.) CHES 2001. LNCS, vol. 2162, pp. 309–318. Springer, Heidelberg (2001)

- 2. Blömer, J., Guajardo, J., Krummel, V.: Provably Secure Masking of AES. In: Handschuh, H., Hasan, M.A. (eds.) SAC 2004. LNCS, vol. 3357, pp. 69–83. Springer, Heidelberg (2004)

- 3. Clavier, C., Coron, J.-S., Dabbous, N.: Differential power analysis in the presence of hardware countermeasures. In: Paar, C., Koç, Ç.K. (eds.) CHES 2000. LNCS, vol. 1965, pp. 252–263. Springer, Heidelberg (2000)

- Coron, J.-S., Prouff, E., Rivain, M.: Side Channel Cryptanalysis of a Higher Order Masking Scheme. In: Paillier, P., Verbauwhede, I. (eds.) CHES 2007. LNCS, vol. 4727, pp. 28–44. Springer, Heidelberg (2007)

- Goubin, L.: A Sound Method for Switching between Boolean and Arithmetic Masking. In: Koç, Ç.K., Naccache, D., Paar, C. (eds.) CHES 2001. LNCS, vol. 2162, pp. 3–15. Springer, Heidelberg (2001)

- Goubin, L., Patarin, J.: DES and Differential Power Analysis The Duplication Method. In: Koç, Ç.K., Paar, C. (eds.) CHES 1999. LNCS, vol. 1717, pp. 158–172. Springer, Heidelberg (1999)

- Gueron, S., Parzanchevsky, O., Zuk, O.: Masked Inversion in GF(2<sup>n</sup>) Using Mixed Field Representations and its Efficient Implementation for AES. In: Nedjah, N., Mourelle, L.M. (eds.) Embedded Cryptographic Hardware: Methodologies and Architectures, pp. 213–228. Nova Science Publishers (2004)

- 8. Kocher, P.: Timing Attacks on Implementations of Diffie-Hellman, RSA, DSS, and Other Systems. In: Koblitz, N. (ed.) CRYPTO 1996. LNCS, vol. 1109, pp. 104–113. Springer, Heidelberg (1996)

- Kocher, P., Jaffe, J., Jun, B.: Differential Power Analysis. In: Wiener, M.J. (ed.) CRYPTO 1999. LNCS, vol. 1666, pp. 388–397. Springer, Heidelberg (1999)

- Oswald, E., Mangard, S., Pramstaller, N., Rijmen, V.: A Side-Channel Analysis Resistant Description of the AES S-box. In: Gilbert, H., Handschuh, H. (eds.) FSE 2005. LNCS, vol. 3557, pp. 413–423. Springer, Heidelberg (2005)

- Prouff, E., Giraud, C., Aumonier, S.: Provably Secure S-Box Implementation Based on Fourier Transform. In: Goubin, L., Matsui, M. (eds.) CHES 2006. LNCS, vol. 4249. Springer, Heidelberg (2006)

- 12. Rivain, M., Dottax, E., Prouff, E.: Block Ciphers Implementations Provably Secure Against Second Order Side Channel Analysis. Cryptology ePrint Archive, Report 2008/021 (2008), http://eprint.iacr.org/

# A Distribution of the Differentials

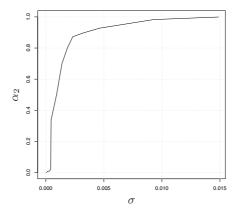

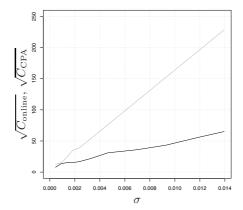

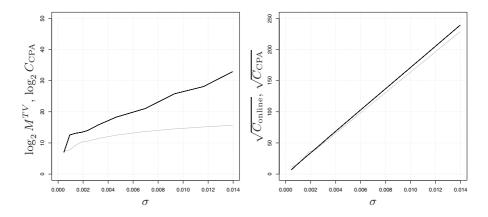

In this section, we investigate the distribution of the differential  $\Delta_k$  when the attack targets a masked bit  $b = f(X, k^*) \oplus R$  where R is a random bit satisfying  $P[R = 0] = \frac{1}{2} + \varepsilon$ . Our analysis includes the unmasked case by setting  $\varepsilon$  to  $\frac{1}{2}$ .

We make the usual assumption that the leakage has a Gaussian distribution:

$$L(b) \sim \mathcal{N}\left(\mu - \frac{\delta}{2}(-1)^b, \sigma^2\right) ,$$

(14)

where  $\mu$ ,  $\delta$  and  $\sigma$  are constants and  $\delta$  equals E[L(1)] - E[L(0)].

The leakage measurement  $l_i$  obtained for the  $i^{th}$  encryption can thus be expressed as:

$$l_i = \mu - \frac{\delta}{2} (-1)^{b_i^{\star} + r_i} + \eta_i , \qquad (15)$$

where, for the  $i^{\text{th}}$  encryption,  $b_i^{\star}$  is the unmasked value of b (i.e.  $b_i^{\star} = f(x_i, k^{\star})$ ),  $r_i$  is the mask value and  $\eta_i$  is the noise in the leakage measurement.

We make the additional assumption that for every key hypothesis k, the sequence of guesses satisfies:  $\#\{i; b_i = 0\} = \#\{i; b_i = 1\} = N/2$ . This assumption is realistic since the functions  $f(\cdot, k)$  are usually balanced (i.e.  $\#\{x; f(x, k) = 1\} = \#\{x; f(x, k) = 0\}$ ) and since the  $x_i$ 's are usually uniformly distributed. It allows us to rewrite (6) as:

$$\Delta_k = -\frac{2}{N} \left( \sum_{i=1}^N (-1)^{b_i} l_i \right) . \tag{16}$$

This relation together with (15) leads to:

$$\Delta_k = \frac{\delta}{N} \sum_{i=1}^N (-1)^{b_i + b_i^* + r_i} - \frac{2}{N} \sum_{i=1}^N (-1)^{b_i} \eta_i$$

$$= \frac{\delta}{N} \left( \sum_{\substack{i=1 \\ b_i = b_i^*}}^N (-1)^{r_i} - \sum_{\substack{i=1 \\ b_i \neq b_i^*}}^N (-1)^{r_i} \right) - \frac{2}{N} \sum_{i=1}^N (-1)^{b_i} \eta_i$$

Recalling that  $\alpha$  is the *ratio* of the  $b_i$ 's that are wrongly predicted (i.e.  $\alpha = \#\{i; b_i \neq b_i^*\}/N$ ) and after rewriting  $(-1)^{r_i}$  as  $1 - 2r_i$ , we get:

$$\Delta_k = \delta(1 - 2\alpha) + \frac{2\delta}{N} \left( \sum_{\substack{i=1\\b_i \neq b_i^*}}^N r_i - \sum_{\substack{i=1\\b_i = b_i^*}}^N r_i \right) - \frac{2}{N} \sum_{i=1}^N (-1)^{b_i} \eta_i .$$

Since  $r_i$  is distributed over  $\mathbb{F}_2$  with  $P[r_i = 1] = 1/2 - \varepsilon$  then for every  $I \subseteq \{1, \dots, N\}$ , the sum  $\sum_{i \in I} r_i$  has a binomial distribution with parameter  $(\#I, 1/2 - \varepsilon)$ . Moreover, since  $\eta_i$  has a Gaussian distribution  $\mathcal{N}(0, \sigma^2)$ , then the sum  $\sum_{i=1}^{N} (-1)^{b_i} \eta_i$  has a Gaussian distribution  $\mathcal{N}(0, N\sigma^2)$ . This way, we obtain:

$$\Delta_k \sim \mathcal{N}\left(\delta(1-2\alpha), \frac{4\sigma^2}{N}\right) + \frac{2\delta}{N}\mathcal{B}\left(\alpha N, \frac{1}{2} - \varepsilon\right) - \frac{2\delta}{N}\mathcal{B}\left((1-\alpha)N, \frac{1}{2} - \varepsilon\right) .$$

After approximating  $\mathcal{B}(n,p)$  by  $\mathcal{N}(np,np(1-p))$  (which is almost exact when  $n \geq 30, np > 5$  and n(1-p) > 5), we finally get:

$$\Delta_k \sim \mathcal{N}\left(2\varepsilon \times \delta(1-2\alpha), \frac{4\sigma^2 + \delta^2(1-4\varepsilon^2)}{N}\right)$$

.

### J.-S. Coron et al.

14

This relation shows that the biased masking results in a reduction of the expectation of  $\Delta_k$  and in an increase of its variance. The expectation is divided by a factor  $1/2\varepsilon$  while its variance is multiplied by a factor  $1+\delta^2(1-4\varepsilon^2)/\sigma^2$ . When the leakage signal-to-noise ratio is low, i.e.  $\sigma \gg \delta$ , then the biais has a weak influence on the variance and its main effect is the reduction of the expectation. According to [3] this results in an increase of the number of required leakage measurements by a factor  $(1/2\varepsilon)^2$ . If the leakage signal-to-noise ratio is not that low, the increase of the variance is significant and the number of required leakage measurements is multiplied by  $(1/2\varepsilon)^2(1+\delta^2(1-4\varepsilon^2)/\sigma^2)$ .

# Collision-Based Power Analysis of Modular Exponentiation Using Chosen-Message Pairs

Naofumi Homma<sup>1</sup>, Atsushi Miyamoto<sup>1</sup>, Takafumi Aoki<sup>1</sup>, Akashi Satoh<sup>2</sup>, and Adi Shamir<sup>3</sup>

<sup>1</sup> Graduate School of Information Sciences, Tohoku University {homma,miyamoto}@aoki.ecei.tohoku.ac.jp, aoki@ecei.tohoku.ac.jp

<sup>2</sup> National Institute of Advanced Industrial Science and Technology akashi.satoh@aist.go.jp

<sup>3</sup> Weizmann Institute of Science adi.shamir@weizmann.ac.il

Abstract. This paper proposes new chosen-message power-analysis attacks against public-key cryptosystems based on modular exponentiation, which use specific input pairs to generate collisions between squaring operations at different locations in the two power traces. Unlike previous attacks of this kind, the new attacks can be applied to all the standard implementations of the exponentiation process: binary (left-to-right and right-to-left), m-ary, and sliding window methods. The SPA countermeasure of inserting dummy multiplications can also be defeated (in some cases) by using the proposed attacks. The effectiveness of the attacks is demonstrated by actual experiments with hardware and software implementations of RSA on an FPGA and the PowerPC processor, respectively. In addition to the new collision generation methods, a high-accuracy waveform matching technique is introduced to detect the collisions even when the recorded signals are noisy and the clock has some jitter.

**Keywords:** side-channel attacks, power-analysis attacks, RSA, modular exponentiation, waveform matching.

# 1 Introduction

Physical attacks on cryptographic modules using side-channel information are attracting extensive attention. In order to reveal the secret parameters, the power dissipation, the electromagnetic radiation, or the operating times related to internal operations are analyzed. Two of the best known attacks are Simple Power Analysis (SPA) and Differential Power Analysis (DPA) proposed by Kocher et al. [1,2].

The original concept of side-channel attacks against modular exponentiation [3] is to look for some physical phenomena which differentiates between multiplication and squaring operations. Messerges presented a variety of power-analysis attacks against RSA with some experimental results [4]. However, most of the

E. Oswald and P. Rohatgi (Eds.): CHES 2008, LNCS 5154, pp. 15–29, 2008.

<sup>©</sup> International Association for Cryptologic Research 2008

implementations of modular exponentiation nowadays use the same sequence of instructions to implement multiplications and squarings, and for random inputs, it is very difficult to distinguish between these two operations. In order to cause secret information to leak via the power waveforms, chosen-message attacks that use specific data specialized for a particular cryptographic module were proposed [5,6,7,8,9,10].

The timing attacks against RSA with Montgomery multiplication [11] and/or CRT algorithm in [5,6] measures the operating times caused by extra calculations depending on input data. The SPA with adaptively chosen messages [7] can be applied to an RSA implementation using CRT based on Garner's algorithm, in which an extra modular reduction is performed at the end of the operation according to the input data. The DPA using the Hamming weight of an intermediate value [8] was also applied to RSA with CRT. These attacks focused on specific RSA implementations, and thus information about the implementation is indispensable to reveal the secret keys. The first three attacks can be defeated by inserting dummy operations, and the DPA of [8] cannot be applied to implementations using the Montgomery algorithm.

Over the last few years, several researchers have proposed to use a power analysis technique which is a mixture of the simple and the differential approaches. This technique compares two segments of power consumption data (within a single execution or in two different executions) and uses the result to determine whether the values operated on were the same or different. For example, when we perform two multiplications  $a \times b$  and  $c \times d$ , we expect the power consumption curves to be similar when a = c and b = d, and different in all other cases. This can give us a simple equality oracle, even though it may be extremely difficult to determine the actual values of a, b, c, and d from the complex waveforms. This is not a standard SPA technique since we do not try to understand the details of each waveform, and it is not a standard DPA since it is not based on the statistical analysis of large collections of power traces. We propose to call such attacks on pairs of waveforms CPA (Comparative Power Analysis).

One of the simplest attacks of this type was proposed by Yen et al [10]. It uses the particular input data of N-1 where N is the modulus, which has the special property that all its powers are either 1 or -1. However, a simple countermeasure is to block the special message N-1, and the attack can only be applied to implementations using a left-to-right binary method.

Another attack of this type is the "doubling attack" of Fouque and Valette [9]. They used the two related input messages X and  $X^2$  to cause collisions between adjacent time frames in the two power waveforms, where squaring operations are performed. Since every message X can be part of such a message pair, it is harder to block potentially harmful messages. As in the case of Yen's method, these attacks can only be applied to the left-to-right binary method, and the authors make this point explicit in the title of their paper: "The Doubling Attack - Why Upwards is Better than Downwards".

In this paper we propose new power-analysis attacks using input pairs which can be successfully applied to all the standard implementations of the exponentiation function, including both left-to-right and right-to-left binary methods, m-ary (window), and sliding window methods. The major new element of these attacks is the observation that an attacker can easily choose pairs of messages that generate collisions between their power traces at arbitrary time frames (which need not be the same or adjacent) even though he does not know the factorization of the modulus and thus cannot extract modular roots. Information about the locations of such non-adjacent collisions in the power traces is then used to identify the bit pattern of the secret exponent. In the proposed attack, the relationship between the two input messages can cope flexibly with the many variants of exponentiation algorithms, including those which were immune to previous attacks.

We demonstrate the practical effectiveness of the proposed attacks against hardware and software implementations of RSA using a Xilinx FPGA with a PowerPC processor core. In this experiment, a high-accuracy waveform matching technique is introduced to find collisions between squaring patterns that appear at different time frames even when the signal is noisy and the clock has some jitter.

The remainder of this paper is organized as follows: Section 2 presents an overview of modular exponentiation algorithms and describes power-analysis attacks using a chosen-message pair. In Section 3, the new power-analysis attacks using chosen-message pairs against binary and *m*-ary methods are proposed. Section 4 describes the experimental results using actual RSA hardware and software implementations. Finally, Section 5 contains some concluding remarks.

# 2 Preliminary and Related Attacks

# 2.1 Modular Exponentiation Algorithms

Modular exponentiation is one of the most important arithmetic operations for public-key cryptography, such as the RSA scheme and the ElGamal encryption scheme, and for the Diffie-Hellman key agreement. Basically, there are two types of efficient exponentiation algorithms: binary methods and m-ary (or window) methods [12,13].

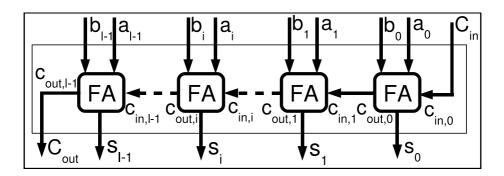

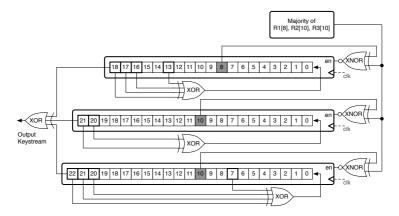

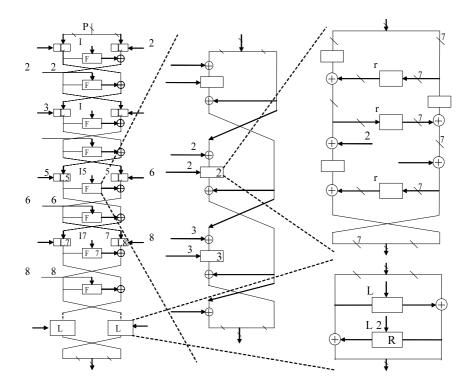

The binary method performs multiplications and squarings sequentially according to the bit pattern of the exponent. There are two variations of the algorithm. The left-to-right binary method starts at the exponent's MSB and works downward. The right-to-left binary method, on the other hand, starts at the exponent's LSB and works upward. **ALGORITHM 1** shows the left-to-right binary method, where k indicates the bit length of the secret keys. Each multiplication (or squaring) operation requires a large number of clock cycles due to the long operand length depending on the implementation. The binary method is frequently used in smartcards and embedded devices, due to its simplicity and low resource consumption.

The m-ary method processes more than one bit of the exponent in each iteration cycle, in which the exponent uses a representation with base m. **ALGO-RITHM 2** shows the m-ary method in which the exponent is processed from

# ALGORITHM 1

### LEFT-TO-RIGHT BINARY METHOD

| Input:         | X, N,                        |  |  |

|----------------|------------------------------|--|--|

|                | $E = (e_{k-1},, e_1, e_0)_2$ |  |  |

| Output         | $: Z = X^E \mod N$           |  |  |

| 1: Z:          | = 1;                         |  |  |

| 2 : <b>for</b> | i = k - 1 downto 0           |  |  |

| 3:             | $Z := Z * Z \mod N;$         |  |  |

| 4: i           | if $(e_i = 1)$ then          |  |  |

| 5:             | $Z := Z * X \mod N;$         |  |  |

| 6: <b>•</b>    | end if                       |  |  |

| 7: en          | d for                        |  |  |

# **ALGORITHM 2**

m-ary method

```

X. N.

Input:

E = (e_{k-1}, ..., e_1, e_0)_{2^m},

for m \geq 1.

Output: Z = X^E \mod N

1:

q_0 := 1;

for i = 1 to 2^m - 1

2:

g_i := g_{i-1} * X; \quad -g_i = X^i

4:

end for

Z := 1;

5:

for i = k - 1 downto 0

for l=1 to m

7:

8:

Z := Z * Z \mod N;

9:

end for

10:

Z := Z * g_{e_i} \mod N;

11:

end for

```

the MSB down to the LSB. The powers  $g_i \mod N$   $(i=0,1,2,...,2^m-1)$  are precomputed and used in multiplication. The intermediate value Z is raised to the power of  $2^m$  by repeating the squaring operation m times. The m-ary method requires fewer clock cycles but more memory resources compared with the binary methods, and thus is often used for software implementation on processors with large memory resources. The sliding window method is an extension of the m-ary method to reduce the amount of pre-computation by using the presence of zero bits in the exponent.

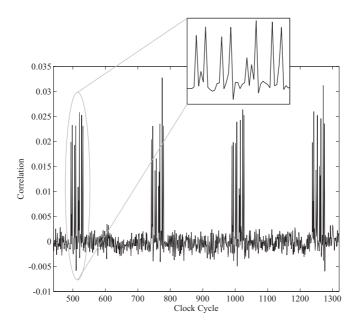

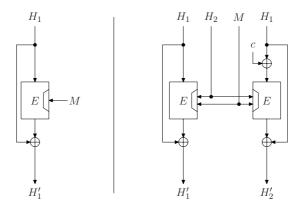

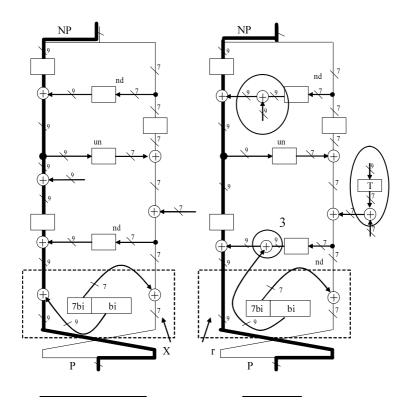

# 2.2 SPA Using a Chosen-Message Pair against Modular Exponentiation

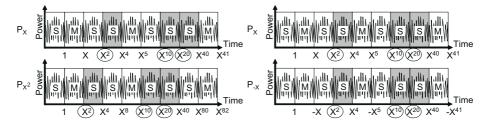

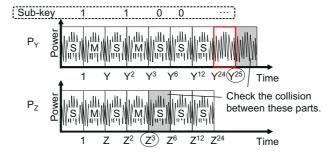

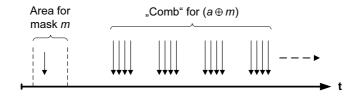

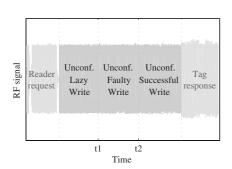

The doubling attack [9] uses the two related inputs X and  $X^2$ . The secret exponent is revealed by detecting collisions of squaring operations in two power traces. Fig. 1 illustrates an image of the doubling attack against the left-to-right binary method in **ALGORITHM 1** with the secret key exponent of "101001..." The doubling attack can generate a collision between a squaring operation at the i+1-th cycle in the power trace of X and a squaring operation at the i-th cycle in that of  $X^2$  only if the corresponding key bit  $e_i$  is 0. The collision for squaring is detected by comparing the power traces, and thus we do not have to know the intermediate data being processed. The doubling attack works on modular exponentiation based on left-to-right binary methods including those using the blinding countermeasures shown in [14].

A different attack which uses the message pair X and -X (= N-X mod N) was proposed by Yen et al [10]. Fig. 2 illustrates an image of this attack against the left-to-right binary method. When the key bit  $e_i$  is 0, a collision between power traces can be observed for the two squaring operations during the same iteration cycle.

Fig. 1. Doubling attack. [9]

Fig. 2. Yen's attack. [10]

Both attacks exploit the fact that the values which are squared depend on the bits of the secret exponent. As mentioned in [9], it is hard to apply the attack to exponentiation algorithms such as right-to-left algorithms and window methods that perform squaring operations independently of the secret exponent.

# 3 The New Attacks

The above two attacks generate collisions of squaring operations at the adjacent or the same time frames in two power traces. In contrast, the proposed attacks generate a collision between two power traces at two arbitrary time frames by using two input messages with a more flexible relationship. One input gives a power trace including an unknown (multiplication or square) operation depending on a target key bit to be estimated, which is called a target operation. The other input gives a power trace including a square operation, the input of which can be determined by the known sub-key bits, referred to as the reference operation. The partial traces for the target and reference operations are called target and reference waveforms, respectively. The collision between the target and reference waveforms is used to estimate the target key bit.

Our attacks provide direct and backward estimations of the key exponent using the collision. The direct estimation simply compares the target (squaring or multiplication) operation with the reference (squaring) operation to identify the target operation corresponding to the key bit. The backward estimation identifies the target operation by comparing a squaring operation following the target operation with the reference operation. Unlike all the previous techniques, these new estimation techniques can be applied to all the standard exponentiation techniques (including both left-to-right and right-to-left binary methods, m-ary methods and the sliding window methods).

The simple trick we use in order to generate a collision at any pair of locations in two power traces is to find a solution for any equation of the form  $Y^{\alpha} = Z^{\beta} \mod N$ , where  $\alpha$  and  $\beta$  are given constants. Note that the attacker does not know the factorization of N and thus cannot solve this equation by extracting modular roots. However, he can choose an arbitrary value R and compute  $Y = R^{\beta} \mod N$  and  $Z = R^{\alpha} \mod N$ , which is clearly a solution for the equation. This method is also applicable for CRT implementation that uses the prime

Fig. 3. Attack on the binary method (direct estimation)

factors p and q of N as the moduli since the message pair Y and Z satisfies  $Y^{\alpha} = Z^{\beta} \mod p$  and  $Y^{\alpha} = Z^{\beta} \mod q$ .

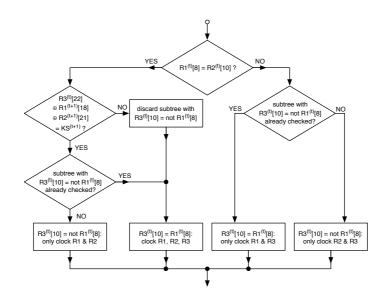

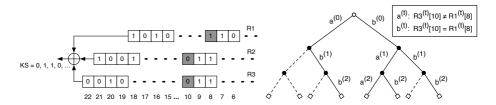

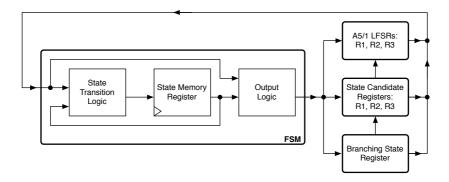

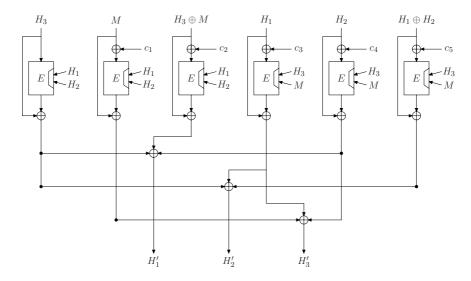

# 3.1 Attack on Binary Methods

First, the direct estimation of the binary method shown in **ALGORITHM 1** is described. Suppose that the sub-key bits  $E^{(j)}$  (=  $e_{k-1}, ..., e_{k-j}$ ) of the secret exponent E have already been obtained. In order to estimate the next key bit  $e_{k-(j+1)}$ , a message pair is used, which causes a collision between the target and reference operations performed at different time frames. If a collision is observed, the target operation is a squaring (i.e.,  $e_{k-(j+1)} = 0$ ). If no collision is observed, then the operation is a multiplication (i.e.,  $e_{k-(j+1)} = 1$ ). Once  $e_{k-(j+1)}$  is obtained, the remaining bits  $e_{k-(j+2)}, ..., e_0$  are sequentially computed in the same manner.

The message pair Y and Z is given as  $Y^{\alpha} = Z^{\beta}(Y \neq Z)$ , where the  $\alpha$  and  $\beta$  satisfy

$$\alpha = 2E^{(j)},\tag{1}$$

$$\beta = \left| \frac{\alpha}{2^t} \right| \ (0 \le t \le j), \tag{2}$$

respectively. Here,  $Y^{\alpha}$  is the input for the target operation performed by  $e_{k-(j+1)}$ , and  $Z^{\beta}$  is the input for the reference operation. If  $e_{k-(j+1)}=0$ , the operation of  $Y^{\alpha}$  is the same as that of  $Z^{\beta}$ . In contrast, if  $e_{k-(j+1)}=1$ , the operation of  $Y^{\alpha}$  is a multiplication, and is different from that of  $Z^{\beta}$ . As a result, the bit  $e_{k-(j+1)}$  is obtained by comparing the target waveforms of  $Y^{\alpha}$  and the reference waveform of  $Z^{\beta}$ .

Fig. 3 shows an example of the direct (bit/digit) estimation of **ALGO-RITHM 1**. Suppose that the attacker already knows the first four bits ( $E^{(4)} = 1100_2$ ). In this condition,  $\alpha$  and  $\beta$  are given as  $\alpha = 24$  and  $\beta = 1, 3, 6, 12$ , or 24. In order to estimate the next key bit, a message pair Y and Z, which meets the condition  $Y^{24} = Z^3$  (i.e.,  $\alpha = 24$  and  $\beta = 3$ ) is used. Here,  $Y^{24}$  is the input for the target operation, and  $Z^3$  is the input for the reference operation. If  $\beta = 24$  ( $Y^{24} = Z^{24}$ ), then Y = r and Z = -r. Therefore, this attack is identical to

Fig. 4. Attack on the binary method (backward estimation)

Yen's attack [10]. If  $\beta = 12$  ( $Y^{24} = Z^{12}$ ), then Y = r and  $Z = r^2$ , which is identical to the doubling attack [9]. Thus, these attacks are special cases of the present direct estimation.

Now, the backward estimation of **ALGORITHM 1** is explained. To estimate the key bit  $e_{k-(j+1)}$ , a squaring operation following the target operation for  $e_{k-(j+1)}$  is investigated. Unlike the direct estimation, the bit value of  $e_{k-(j+1)}$  (0 or 1) is estimated first, and the input message pair is then selected so that the power waveform for the squaring following the target operation would match the waveform for the reference operation. Assuming that  $e_{k-(j+1)} = 1$ , the message pair Y and Z is selected so as to meet the condition  $Y^{\alpha+1} = Z^{\beta}$ . If the estimation of  $e_{k-(j+1)}$  is correct, the operating sequence and data for the squaring of  $Y^{\alpha+1}$  are the same as those of  $Z^{\beta}$ , and the two waveforms of the squaring would be identical. In contrast, if the estimation is incorrect, the two square waveforms would be different.

Fig. 4 shows an example of the backward (bit/digit) estimation against the binary method. Assuming that the target key bit is 1, and the message pair is selected to meet the condition  $Y^{25} = Z^3$ . If the estimation is correct, a multiplication  $Y^{24} \times Y$  is performed as the target operation and the result of  $Y^{25}$  is fed to the following squaring. Therefore, the same input values  $Y^{25}$  and  $Z^3$  (=  $Y^{25}$ ) are used for the squaring operations that generate two power waveforms to be compared. If the target key bit is 0, the target operation is squaring, and the input of the following squaring is  $Y^{48}$  (=  $Y^{24\times 2}$ ), which is not equal to  $Z^3$ , and thus the two waveforms for the squaring do not match.

As described above, the direct estimation compares the two waveforms generated by the reference (square) and the target (unknown) operations with the same input data to determine the target operation. In contrast, the backward estimation compares the two waveforms generated by square operations to determine the input data to the squaring following the target (unknown) operation. In order to determine the operation or the data using waveform matching, the proposed method controls the relation between the messages Y and Z as Equations (1) and (2).

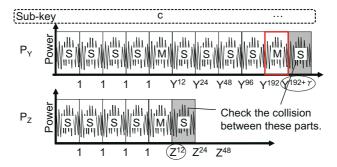

Fig. 5. Attack on the *m*-ary methods (backward estimation)

# 3.2 Attack on m-Ary Methods

The backward estimation has no additional advantage over the direct estimation for attacking the conventional binary method. However, the backward estimation is essential when attacking the m-ary method shown in **ALGORITHM 2**. This algorithm always performs a multiplication after raising the intermediate result to the power of  $2^m$  (i.e., m squaring operations). Therefore, the direct estimation, which detects the multiplication performed only if the corresponding key bit is 1, cannot be applied. Suppose that the m-bit sub-keys  $E^{(j)} = (e_{k-1}, ..., e_{k-j})_{2^m}$  of the secret exponent E have already been obtained. To estimate the next sub-key  $e_{k-(j+1)}$ , the waveform of the squaring following the target multiplication is investigated. At the beginning of the attack, the target sub-key  $e_{k-(j+1)}$  is assumed as  $\gamma$  ( $0 \le \gamma \le 2^m - 1$ ), and the message pair Y and Z is selected to meet the condition  $Y^{\alpha+\gamma} = Z^{\beta}$ , where the  $\alpha$  and  $\beta$  are given as

$$\alpha = 2^m E^{(j)},\tag{3}$$

$$\beta = \left\lfloor \frac{\alpha}{2^{mt}} \right\rfloor \ (0 \le t \le j), \tag{4}$$

respectively. If the estimation is correct  $(e_{k-(j+1)} = \gamma)$ , the input data  $Y^{\alpha+\gamma}$  to the squaring following the target multiplication is the same as the  $Z^{\beta}$  input in the reference squaring, and thus the waveforms for the two squaring operations would match. Even if the estimation is wrong, the correct sub-key can be obtained after  $2^m$  trials at most.

Fig. 5 shows an example of the attack against the m-ary algorithm of **AL-GORITHM 2**, where m=4. When the sub-key  $e_{k-1}=12$  is already known,  $\alpha$  and  $\beta$  can be given by  $\alpha=192$  and  $\beta=12$ . Assuming that  $e_{k-2}$  is  $\gamma$ , a message pair Y and Z is selected to meet the condition  $Y^{192+\gamma}=Z^{12}$ . If the estimation is correct, the input of the squaring  $(Y^{192+\gamma})$  following the target operation is equal to that of the reference squaring  $(Z^{12})$ , and these inputs would make identical waveforms. In this case, the correct sub-key  $e_{k-2}$  can be estimated with at most  $2^4=16$  trials.

Fig. 6. Identification of operations using waveform matching

FPGA Measuring points (Xilinx Virtex-II Pro xc2vp7)

| EXPERIMENTAL FPGA BOARD (SASEBO) |                        |  |  |  |

|----------------------------------|------------------------|--|--|--|

| FPGA                             | Virtex-II Pro xc2vp7   |  |  |  |

| Crystal oscillator               | 24-MHz                 |  |  |  |

| Resistance value                 | 1 Ohm                  |  |  |  |

| Power supply voltage             | 3.3 V                  |  |  |  |

| Experimental equipment           |                        |  |  |  |

| Digital oscilloscope             | Agilent MSO6104A       |  |  |  |

| Probe                            | Coaxial cable (50 Ohm) |  |  |  |

Fig. 7. Evaluation board

Fig. 8. Experimental conditions

# 4 Experiments

# 4.1 Identification of Operations by Waveform Matching

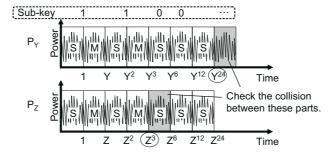

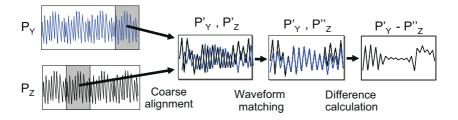

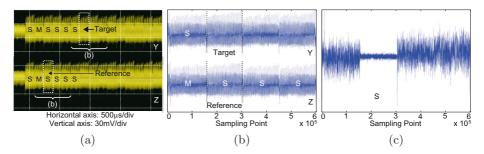

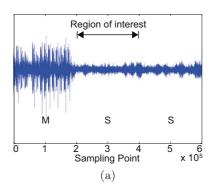

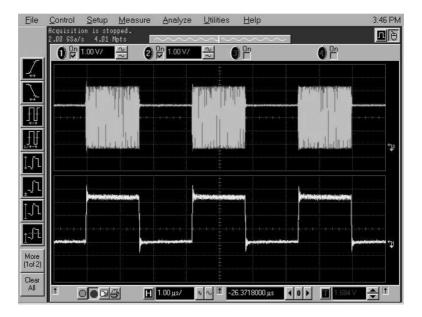

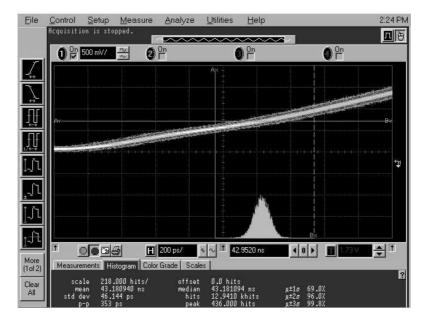

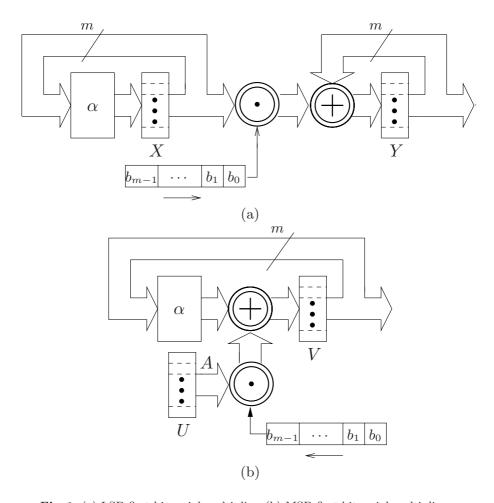

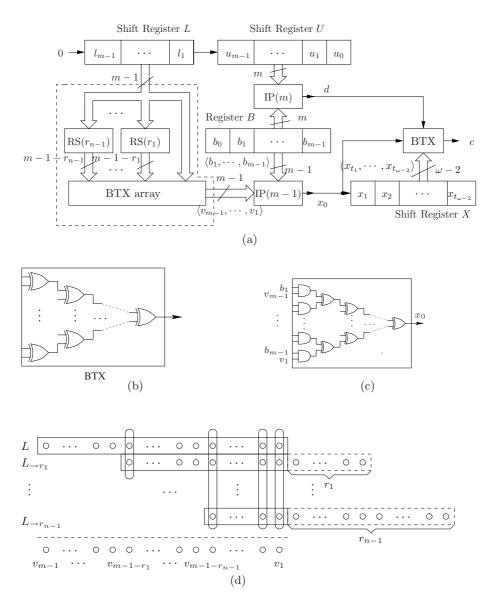

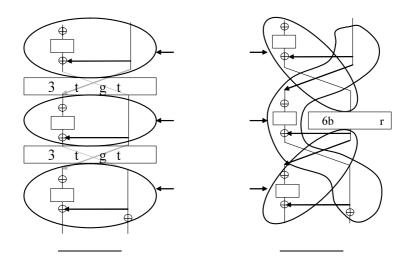

The proposed attacks create collisions between target and reference power waveforms at time frames which can be far apart, whereas previous attacks compare the waveforms at adjacent time frames or at the same time frame, as shown in Figs. 1 and 2. Therefore, a flexible and precise matching technique which can overcome the cumulative effect of clock jitter and noise is crucial for collision detection. In the following, the phase-based waveform matching technique [15], which can match waveform positions with a resolution higher than the sampling resolution, is used. Fig. 6 shows an overview of the identification method. Given two power traces  $P_Y$  and  $P_Z$ , we first cut out the waveform segments that include the target and reference operations,  $P'_Y$  and  $P'_Z$ , respectively. The segments can easily be recognized because each multiplication or square operation consumes less power around the boundaries of the operation. The waveform segments are then aligned precisely using the phase-based waveform matching technique. Finally, the difference between the waveforms is calculated to evaluate the equality of the operations or data being processed.

### 4.2 Experimental Results

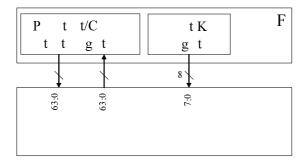

RSA hardware and software using the Montgomery multiplication algorithm were implemented on the Xilinx FPGA platform Side-channel Attack Standard

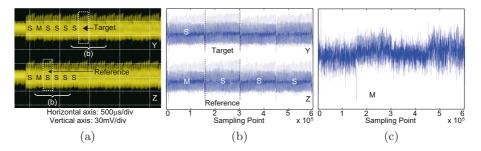

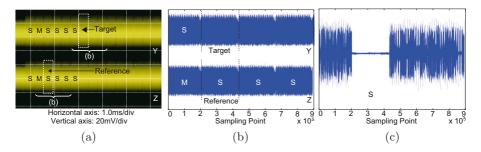

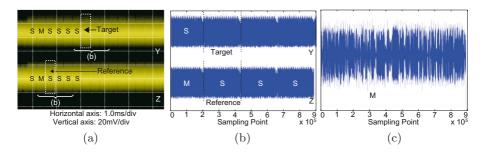

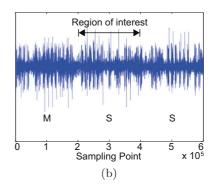

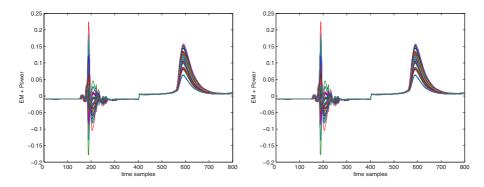

**Fig. 9.** Results of hardware implementation (target: squaring):(a) power traces of Y and Z, (b) waveform segments, and (c) differential waveform

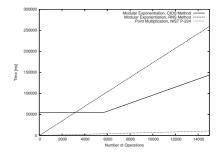

Fig. 10. Results of hardware implementation (target: multiplication):(a) power traces of Y and Z, (b) waveform segments, and (c) differential waveform